This block delays a signal. Similar to the ShiftSample block the first activation of the clock of the output y is delayed by shiftCounter/resolution*interval(u) relative to the input u (interval(u) is the sample period of the clock associated to input u). However, in contrast to ShiftSample, the block provides a buffer for the input values and truly delays the input signal.

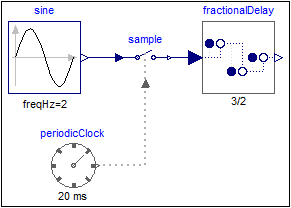

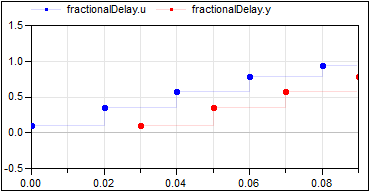

The following

example shows how a sample sine signal is delayed.

|

|

|

| model | simulation result |

The parameter values shiftCounter=3 and resolution=2 are visible at the bottom of the fractionalDelay block.